# Advancing GaN Electronics through Substrate Engineering and Integration

O.R. Meilander, <sup>1</sup> M.A. Ebrish <sup>2</sup>

<sup>2</sup>Department of Electrical & Computer Engineering, Vanderbilt University, Nashville, TN

<sup>1</sup>Department of Interdisciplinary Material Science, Vanderbilt University, Nashville, TN

### **Substrate Selection**

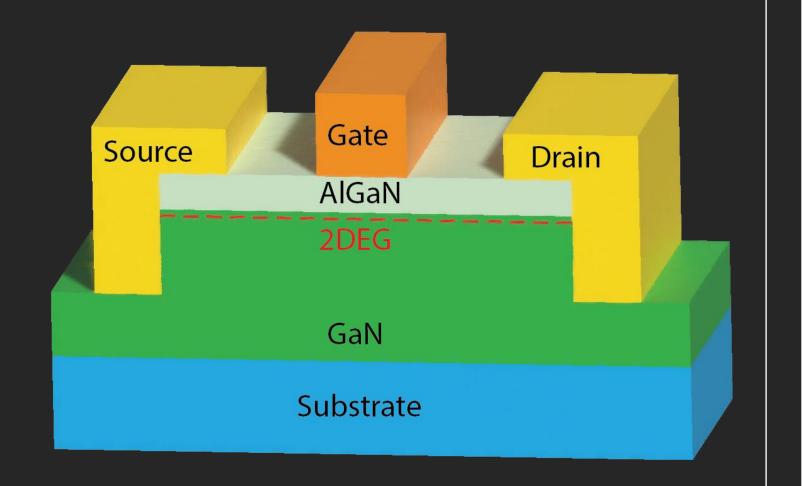

- GaN high electron mobility transistors (HEMT) offer higher performance for high-power and high-frequency applications.

- Free standing GaN is difficult and prohibitively expensive to grow, so heteroepitaxially grown layers are relied upon by industry.

|          | Crystal Structure | Lattice<br>Mismatch (%) | CTE Mismatch<br>(%) |  |

|----------|-------------------|-------------------------|---------------------|--|

| GaN      | НСР               |                         |                     |  |

| Si       | FCC               | -16.5                   | 55                  |  |

| SiC      | НСР               | 3.5                     | 30                  |  |

| Sapphire | НСР               | 16.8                    | -23                 |  |

- While SiC offers the closest crystal properties and the highest thermal conductivity, it is an order of magnitude more expensive.

- Engineered substrate bridge the gap between cost, size, and performance.

### **Substrate Comparison**

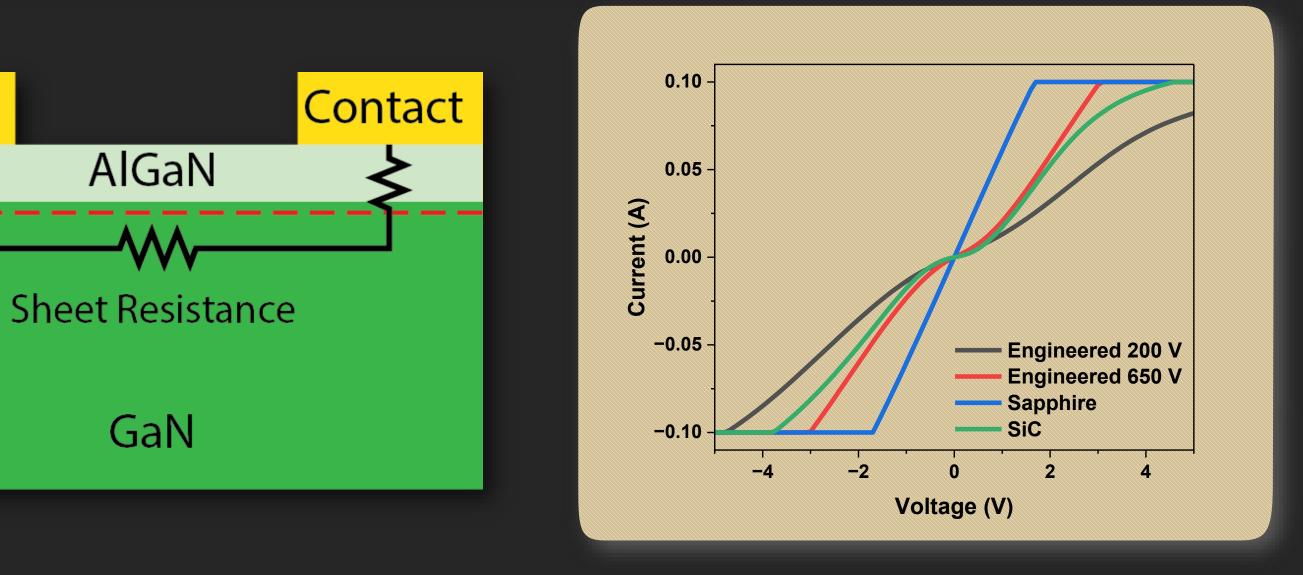

|                        | Sheet Resistance (Ω/ ■) | Specific Contact Resistance $(\mu\Omega\cdot 	ext{cm}^2)$ |

|------------------------|-------------------------|-----------------------------------------------------------|

| QST 200 V (Engineered) | 2630                    | 120                                                       |

| QST 650 V (Engineered) | 1630                    | 212                                                       |

| MSE on Sapphire        | 802                     | 71.9                                                      |

| Qorvo 09 on SiC        | 2440                    | 1430                                                      |

- Different substrates were tested to analyze performance.

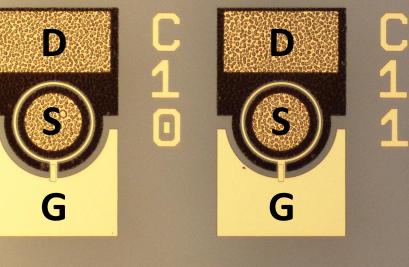

- Circular transmission line measurements (CTLMs) were measured first.

- HEMT on Sapphire showed the lowest sheet and contact resistances.

### **Device Comparison**

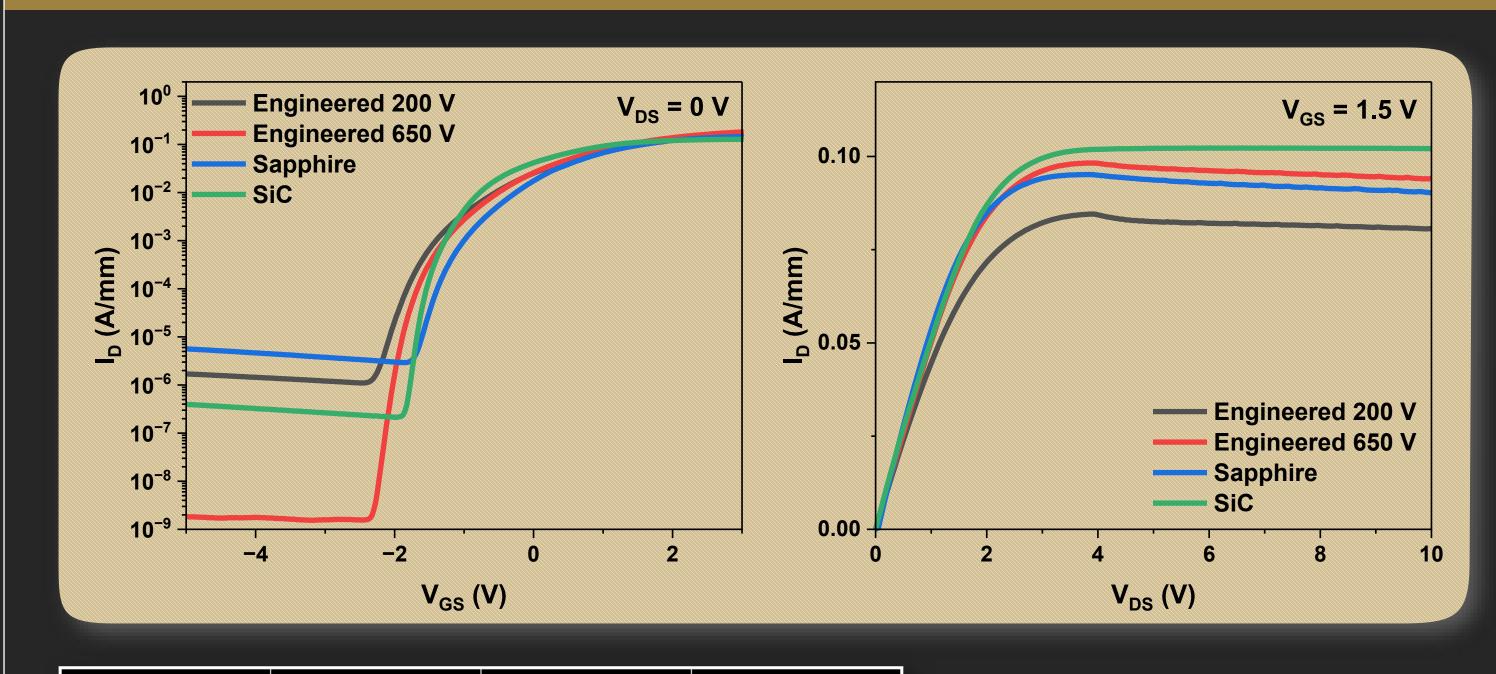

|                        | V <sub>TH</sub> (V) | I <sub>ON</sub> /I <sub>OFF</sub> | $R_{ON}\left(\Omega/\mathrm{mm} ight)$ |

|------------------------|---------------------|-----------------------------------|----------------------------------------|

| QST 200 V (Engineered) | -1.13               | 1.07 x 10 <sup>5</sup>            | 22.4                                   |

| QST 650 V (Engineered) | -1.07               | 7.08 x 10 <sup>7</sup>            | 20.6                                   |

| MSE on Sapphire        | -0.99               | 2.49 x 10 <sup>4</sup>            | 18.0                                   |

| Qorvo 09 on SiC        | -1.06               | 1.47 x 10 <sup>5</sup>            | 17.8                                   |

- While sapphire has low resistance, also has high leakage.

High defectivity.

- SiC has best overall performance and better thermal management.

## Device Design

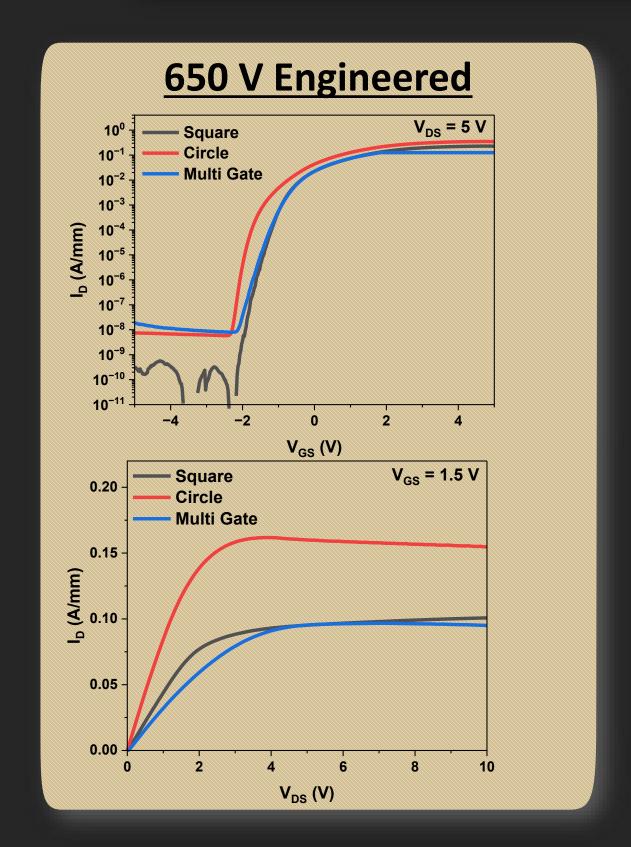

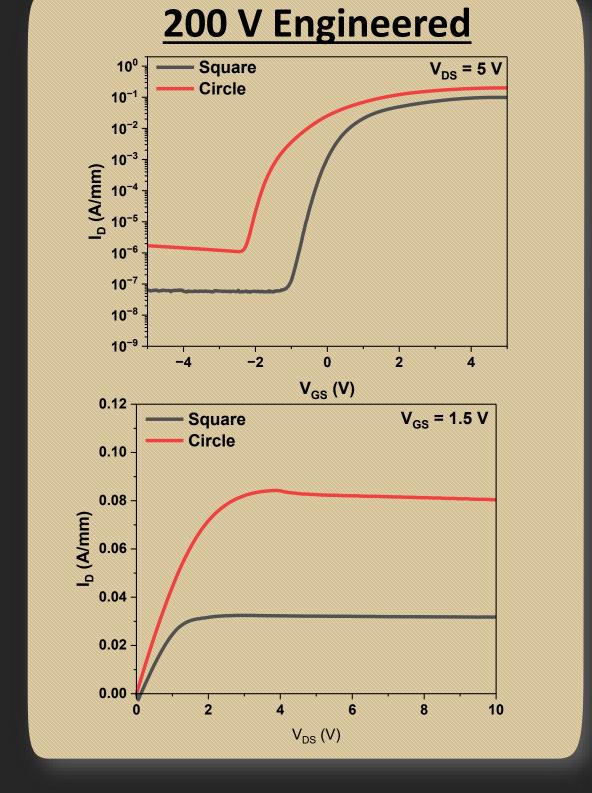

|            | Engineered 650 V    |                                   | Engineered 200 V    |                     |                                   |                        |

|------------|---------------------|-----------------------------------|---------------------|---------------------|-----------------------------------|------------------------|

|            | V <sub>TH</sub> (V) | I <sub>ON</sub> /I <sub>OFF</sub> | $R_{ON}(\Omega/mm)$ | V <sub>TH</sub> (V) | I <sub>ON</sub> /I <sub>OFF</sub> | R <sub>ON</sub> (Ω/mm) |

| Square     | -0.762              | 4.04 x 10 <sup>8</sup>            | 35.4                | -0.382              | 9.97 x 10 <sup>6</sup>            | 35.6                   |

| Circle     | -1.07               | 7.08 x 10 <sup>7</sup>            | 20.6                | -1.13               | 1.07 x 10 <sup>5</sup>            | 22.4                   |

| Multi-Gate | -0.82               | > 1.11 x 10 <sup>7</sup>          | 38.1                |                     |                                   |                        |

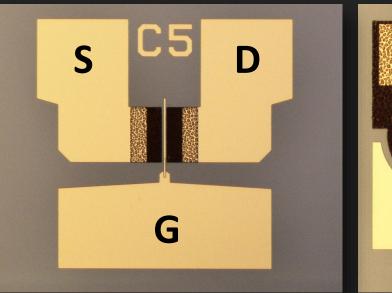

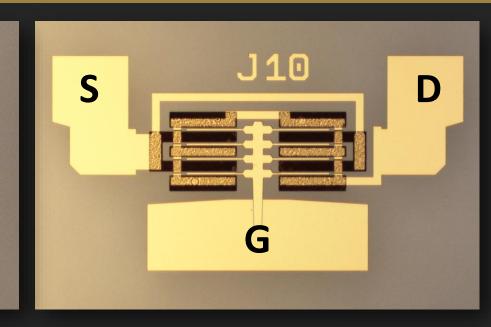

- Different geometries were tested to find the structure with the highest current densities.

- Circular devices consistently have the best performance.

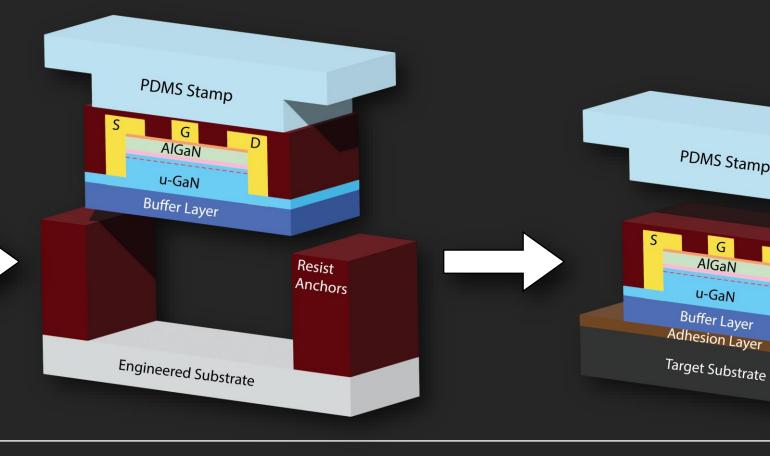

## Heterogenous Integration

- By releasing the device from the engineered substrate and transferring to a target substrate, we can get better performance.

Micro-Transfer Printing gives the perfect platform for scalable integration.

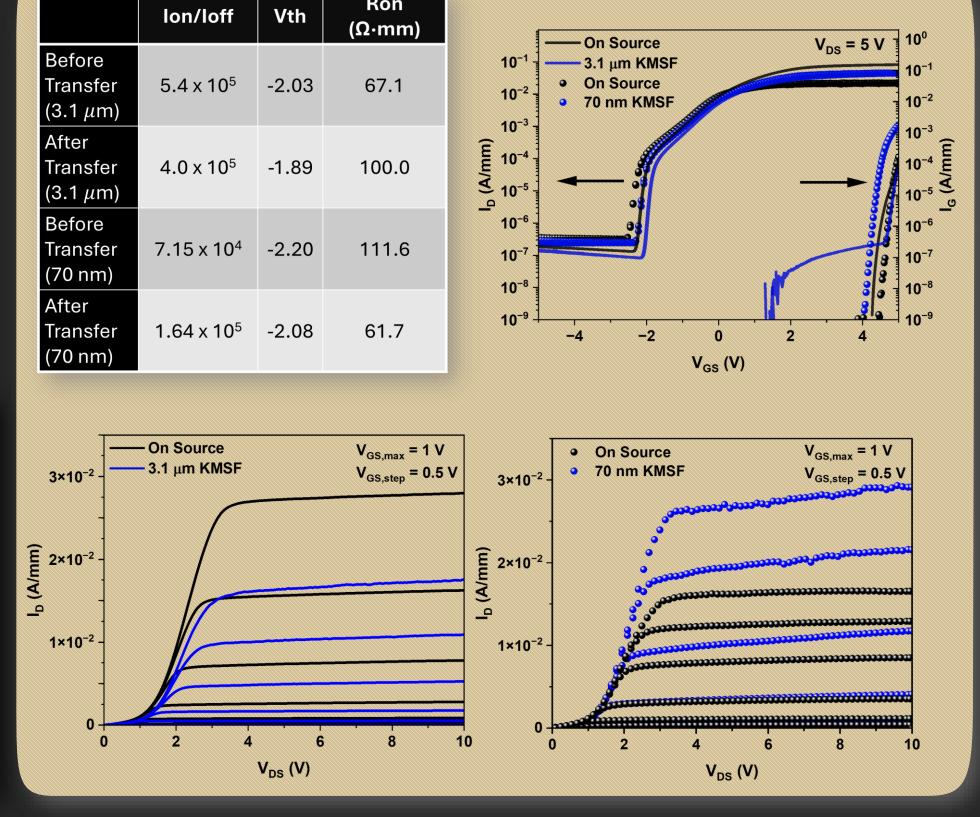

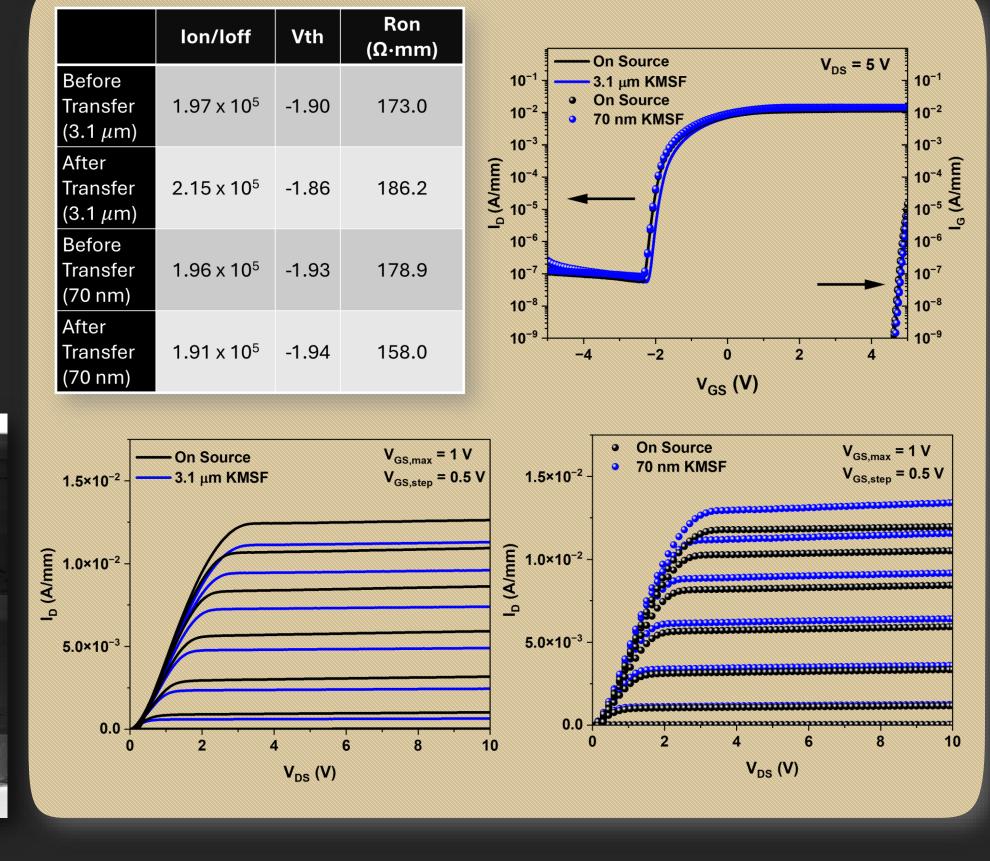

- Different adhesion layer thicknesses tested (3.1  $\mu$ m and 70 nm).

- S G D AlGaN D Resist Anchors

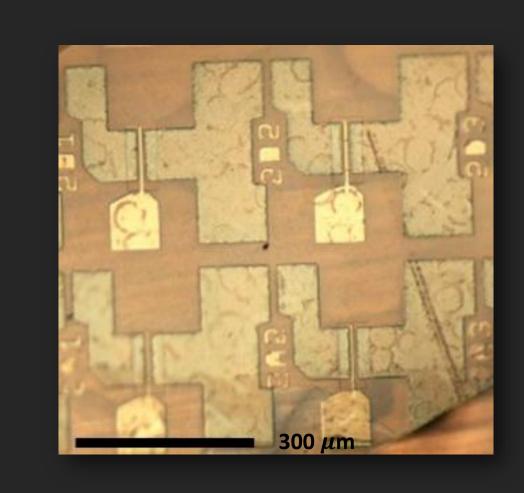

### 650 V Transfer

High (>95%) success rate of the release and transfer was achieved to both adhesion layers.

Buffer Layer

Si (111) Seed Layer

**Engineered Substrate**

Contact

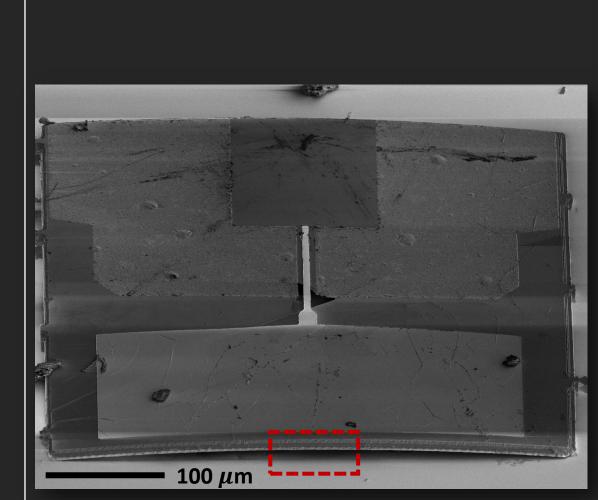

- Minor change in device performance after transfer.

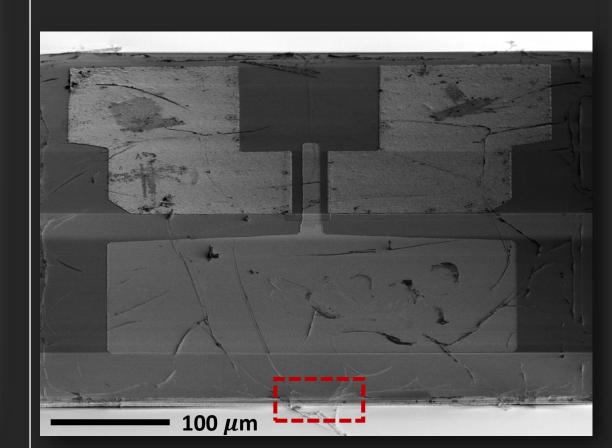

- Stress within the layers led to a 12  $\mu$ m bend after transfer.

### 200 V Transfer

- High (>95%) success rate of the release and transfer was achieved to both adhesion layers.

- Lower stress within the system led to a flat device after transfer.

- Better reliability and minimal change in device performance after transfer.

#### Acknowledgements